IEEE International Conference on Sciences and Techniques of Automatic Control and Computer Engineering

Reduced Instruction Set Computer Design on FPGA

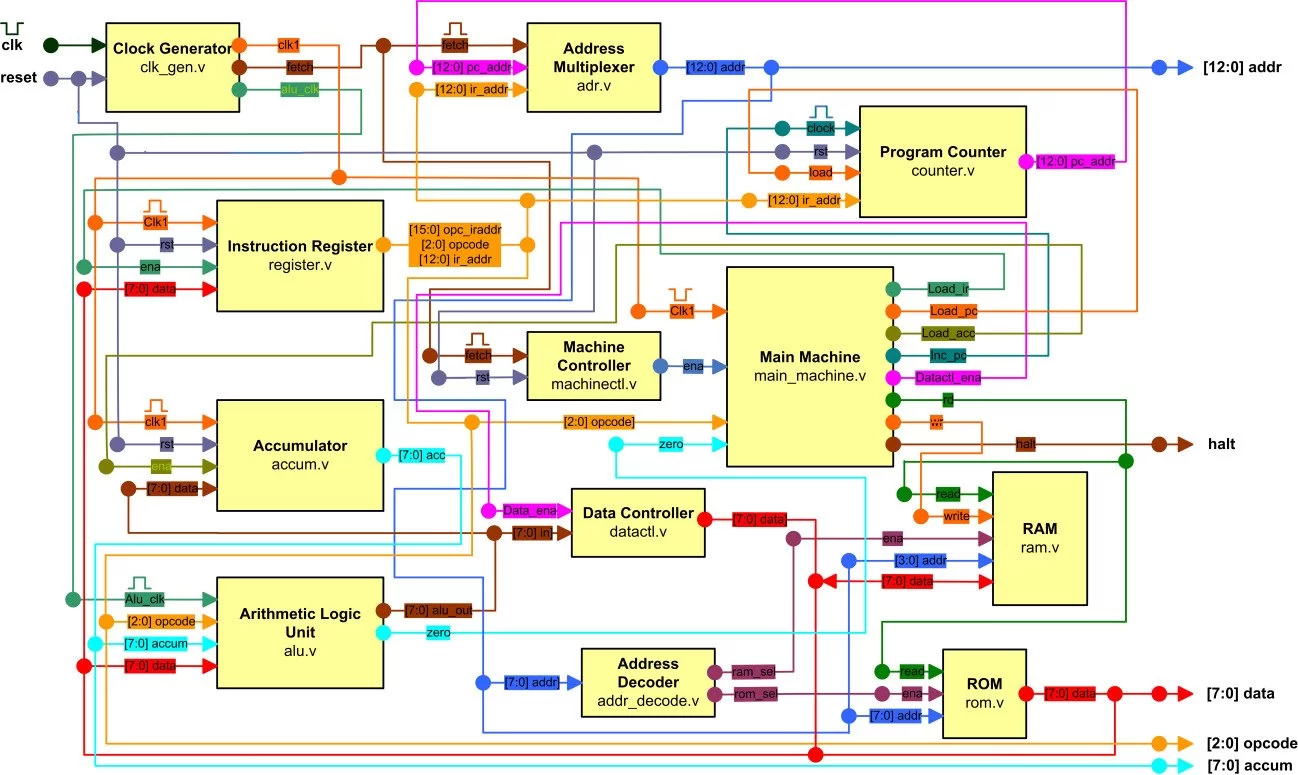

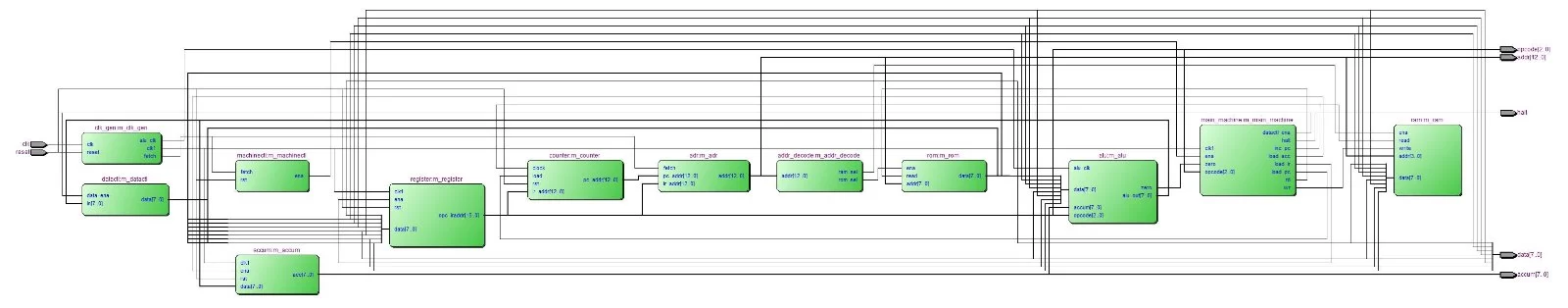

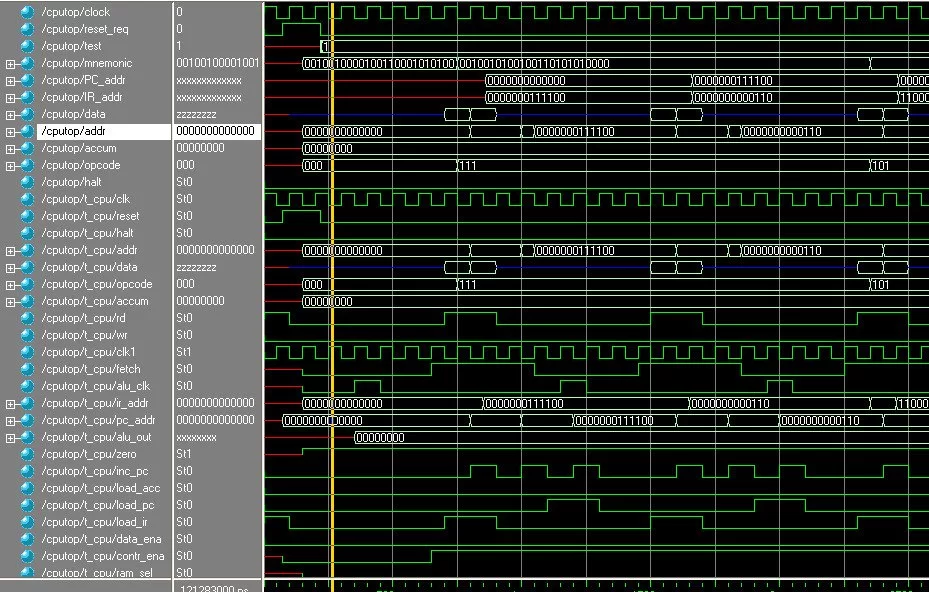

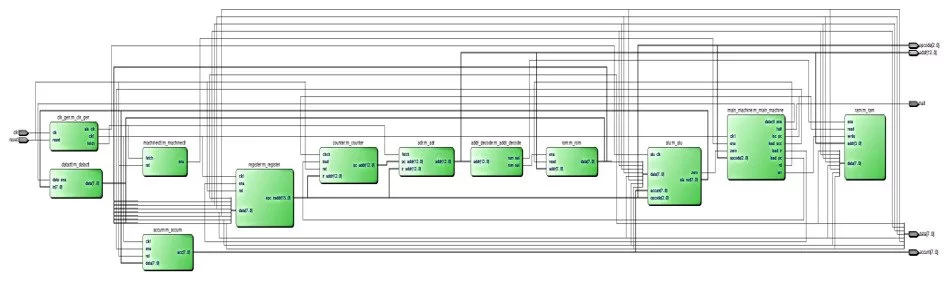

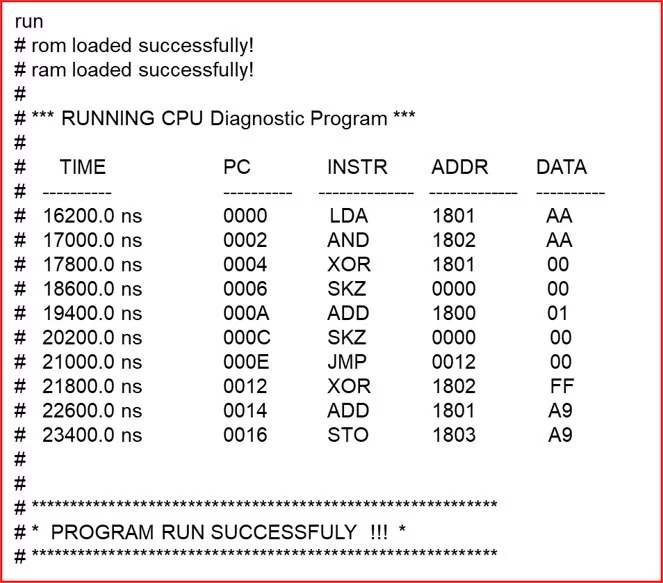

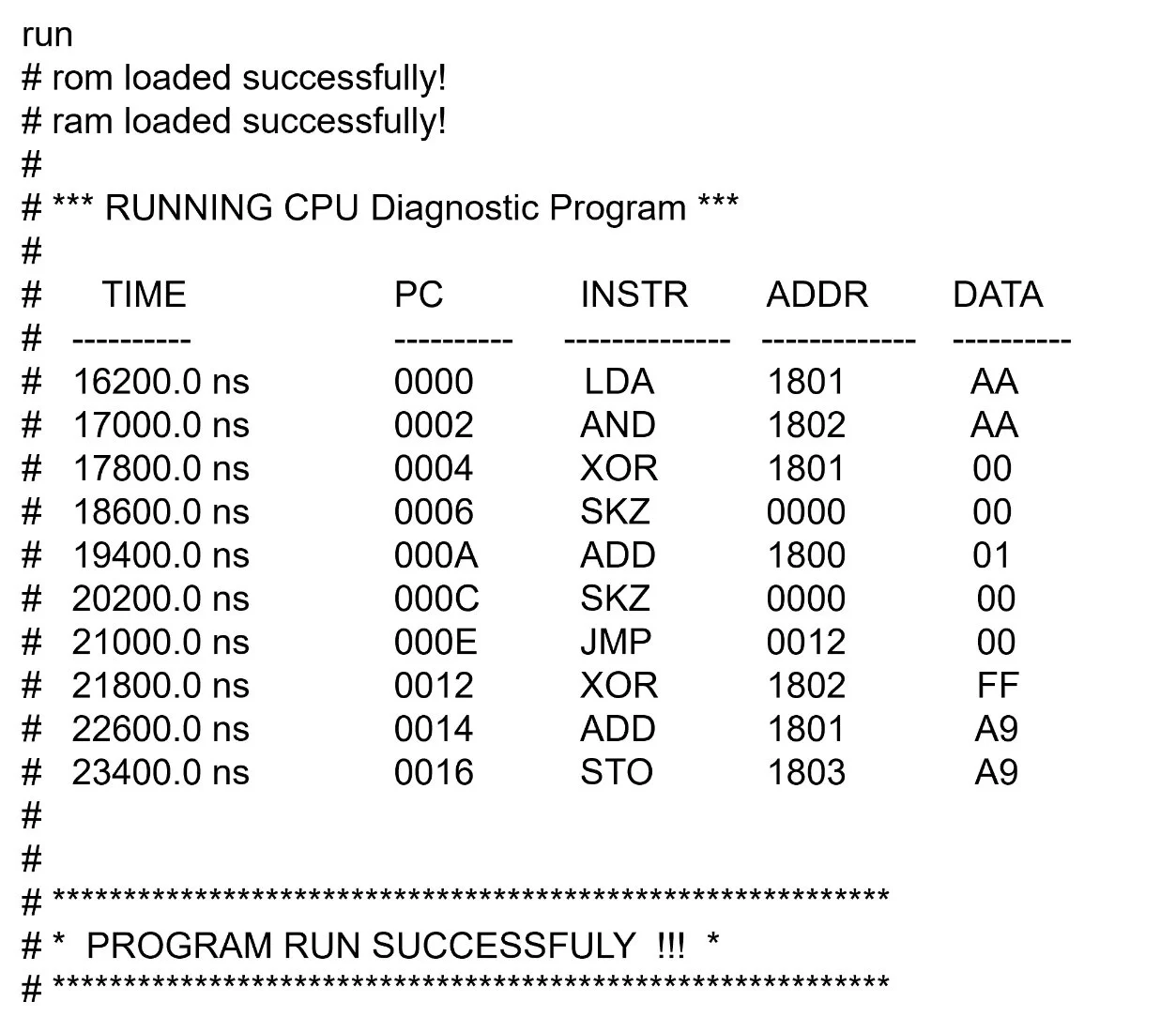

The main purpose of this paper is to design, verify

and implement 16_bit RISC (Reduced Instruction Set Computer)

processor that can be used for many embedded applications.

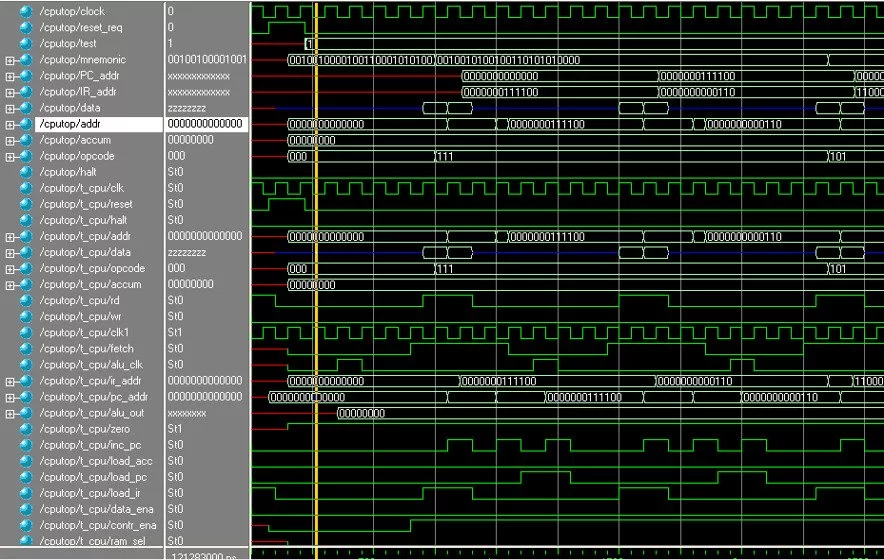

The basic modules of this processor are programmed and

simulated using Verilog HDL (Hardware Description Language),

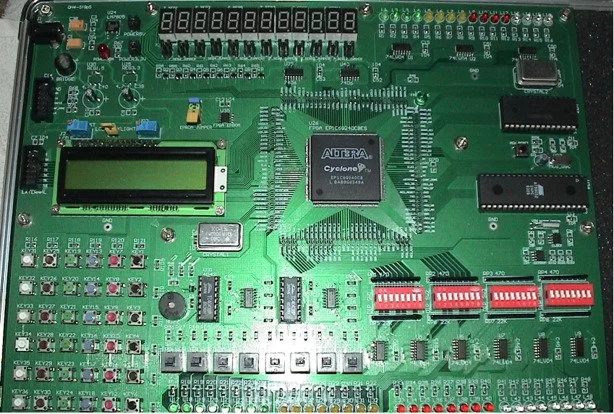

and implemented on Cyclone IV FPGA (Field Programmable

Gate Arrays). Compared with general CPU it is not merely

simplified the instruction set system but also make the computer

structure simpler and more rational through simplifying the

instruction system. Thus, the operating speed is highly improved.

RISC adopts hardwire logic instead of micro-program control

to realize its sequential control signals. The speed of control

sequence generated is much faster than using micro-program

control because it has saved the time of fetching microinstruction.

The philosophy of RISC design presented here favors a smaller

and simpler set of instructions. Those instructions take the

same amount of time to execute. The philosophy of our design

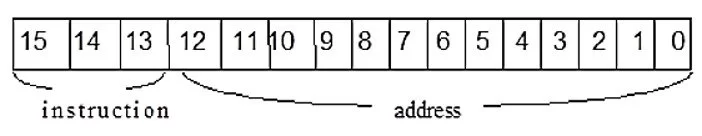

architecture was to keep the instruction set very simple. This in

turn implies that addressing modes supported by instruction set

a further streamlined compared to CISC (Complex Instruction

Set Computer) architectures. Avoiding such addressing modes

must be kept to minimum, which leads to the instructions that

can be executed effectively in eight clock cycles.

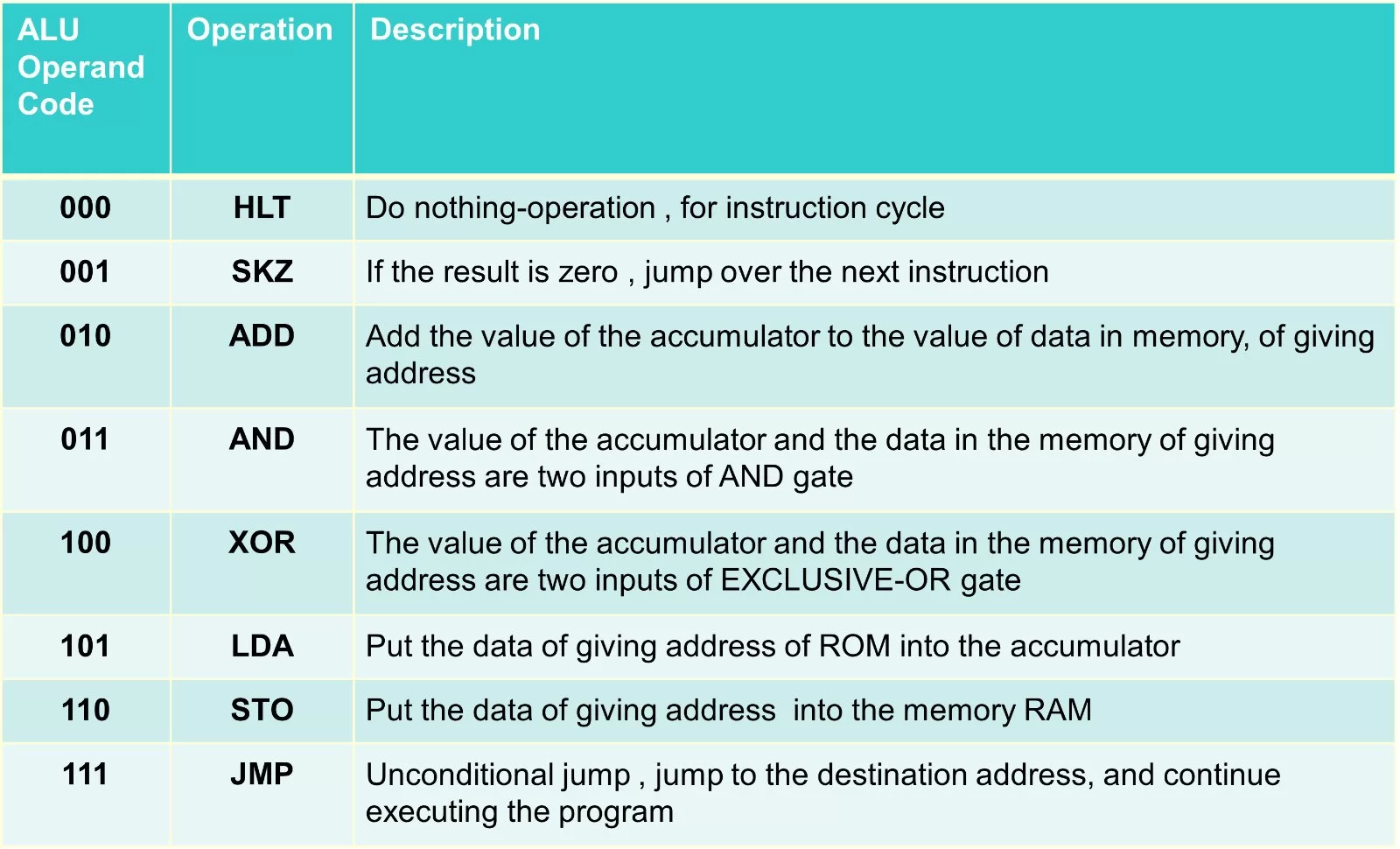

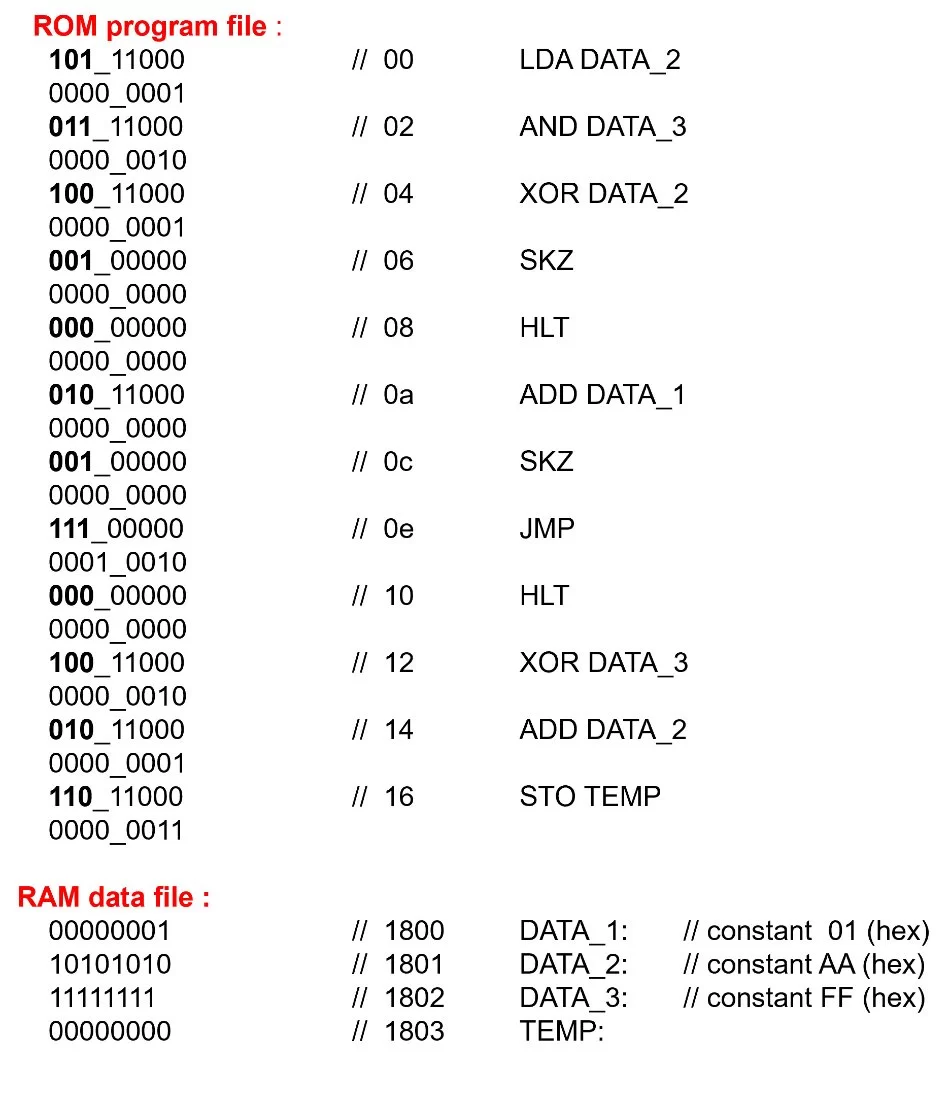

(1)_1732405930.jpg)

التعليقات